Optimizing Logic Gates: Techniques and Trends for Efficient Circuit Design

Logic gate minimization is a critical practice in digital circuit design that optimizes circuits fo…….

Logic gate minimization is a critical practice in digital circuit design that optimizes circuits for improved performance and cost efficiency. This process involves simplifying Boolean expressions to reduce the number of required logic gates, which in turn decreases power consumption, shortens signal delays, and reduces silicon usage in integrated circuits. Minimization techniques like Quine-McCluskey algorithm, Espresso, Petrick's method, and advanced software tools using graph theory and Boolean SAT problems are employed to navigate the complexities of modern digital systems. These methods ensure that designers can achieve efficient solutions for logic gates, whether they are crafting small-scale circuits or designing large-scale computing architectures. The effectiveness of these logic gates directly impacts system performance and is essential for enhancing the capabilities of digital systems across various applications, from high-performance computing to everyday devices. As technology progresses, the integration of sophisticated algorithms, machine learning, and novel materials further advance the functionality of logic gates, supporting the development of complex electronic systems like artificial intelligence and neural networks, while also addressing miniaturization and sustainability challenges.

delve into the intricate process of minimizing logic gates, an essential practice in digital circuit design that optimizes efficiency and performance. This article systematically explores various minimization techniques, starting with a foundational overview. It quantifies the complexity inherent in logic gates and dissects fundamental methods such as Karnaugh Maps and Quine-McCluskey algorithms. It further examines advanced strategies involving algebraic expressions and Boolean Differential Algebraic Expressions (BDAEs). Concluding with a look at practical applications and contemporary trends, this article sheds light on the continuous evolution of logic gate minimization in the digital realm.

- Overview of Logic Gate Minimization Techniques

- Quantifying Complexity in Logic Gates

- Fundamental Minimization Approaches: Karnaugh Maps and Quine-McCluskey Methods

- Advanced Minimization Techniques: Algebraic Expression and Boolean Differential Algebraic Expressions (BDAEs)

- Practical Applications and Modern Trends in Logic Gate Minimization

Overview of Logic Gate Minimization Techniques

Logic gate minimization is a critical aspect of digital circuit design, aimed at reducing the complexity and cost while maintaining functionality. The process involves simplifying Boolean expressions to minimize the number of logic gates used without altering the circuit’s output behavior. Minimization techniques are essential for efficient use of hardware resources, which translates to lower power consumption, reduced delay, and smaller silicon area requirements in integrated circuits.

Several methodologies exist for logic gate minimization, each with its own set of algorithms and heuristics tailored for different scenarios. For instance, techniques like the Quine-McCluskey algorithm and Espresso are automated espression simplification tools that systematically reduce the number of gates by combining equivalent expressions. Petrick’s method is another approach that uses prime implicant selection to arrive at a minimized form. Additionally, modern logic gate minimization often incorporates sophisticated software tools that utilize graph theory and Boolean satisfiability problems (SAT) to achieve optimal solutions in complex digital systems. These tools are indispensable for designers working on everything from small-scale integrated circuits to large-scale computing architectures, where the efficiency of logic gates can significantly impact overall performance.

Quantifying Complexity in Logic Gates

In the realm of digital design, quantifying the complexity of logic gates is a critical aspect for optimizing circuits and enhancing performance. Complexity in this context refers to the number of transistors required to implement a particular logic gate, as well as the intricacies of its operation such as delay, power consumption, and area on the chip. Measuring complexity helps designers assess the efficiency and practicality of a logic gate design. For instance, a simple two-input AND gate has less complexity than a multiplexer with ten inputs, which in turn is simpler than a custom combinational circuit designed to perform multiple operations within a single integrated circuit (IC). Tools like the number of gates, delay through critical paths, and power dissipation are key factors that determine the complexity of logic gates. By systematically analyzing these parameters, designers can make informed decisions to minimize complexity without compromising functionality or performance. This quantification is essential for scaling up designs to larger scales while maintaining optimal operation.

Minimization techniques play a pivotal role in reducing the complexity of logic gate designs. These techniques involve transforming a given logic gate network into an equivalent one with fewer gates, lower power consumption, and reduced delay, yet still performs the same logical operations. Logic gate minimization can be achieved through various methods such as Boolean difference, mapping algorithms, or employing modern Computer-Aided Design (CAD) software that applies heuristic algorithms to simplify logic expressions. The goal is to identify redundancies and replace them with more efficient structures without altering the circuit’s output behavior. This not only leads to cost savings in terms of silicon area but also contributes to the overall efficiency of the digital system, making it a vital practice in the design process of complex integrated circuits.

Fundamental Minimization Approaches: Karnaugh Maps and Quine-McCluskey Methods

Logic gate minimization is a critical process in digital circuit design aimed at reducing the complexity and cost of the circuits while maintaining or improving their performance. Two fundamental techniques for minimizing logic gates are Karnaugh Maps (K-maps) and the Quine-McCluskey method, each offering distinct advantages for different applications.

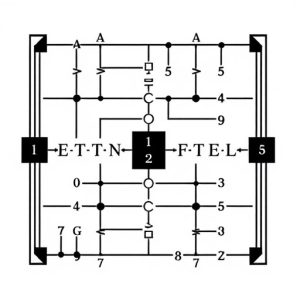

Karnaugh Maps, also known as K-maps, are visual tools used to simplify Boolean functions. They organize the minterms of a function into cells, allowing designers to easily identify and merge adjacent cells that have shared variables in both 1 and 0 states. This process of merging reduces the number of variables required to represent the logic function, thereby minimizing the gates needed for its implementation. K-maps are particularly useful when dealing with small to medium-sized functions due to their simplicity and effectiveness in manual or semi-automated design processes.

The Quine-McCluskey method, on the Essential (or Mapped) Quine-McCluskey Minimization table, is an algorithmic approach that automates the process of logic function simplification. It involves creating a tabular representation of all possible prime implicants and then selecting the minimal cover, which is the smallest set of prime implicants that can represent the original function. This method is highly effective for larger functions, as it can handle a greater number of variables and produce more compact expressions than Karnaugh Maps. The Quine-McCluskey method is an essential technique in automated logic synthesis tools, where it excels in minimizing logic gates to optimize the efficiency and reduce the costs associated with large-scale digital circuitry. Both techniques play a pivotal role in the design of efficient digital circuits composed of logic gates.

Advanced Minimization Techniques: Algebraic Expression and Boolean Differential Algebraic Expressions (BDAEs)

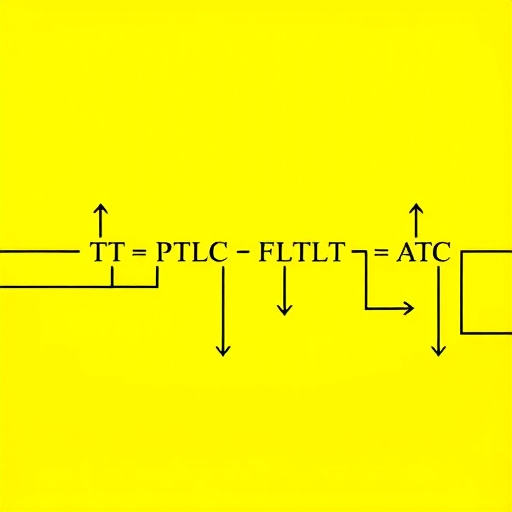

Advanced minimization techniques in digital circuit design play a pivotal role in optimizing the complexity and efficiency of logic gates. Among these, the use of algebraic expressions and Boolean Differential Algebraic Expressions (BDAEs) stands out for its capacity to reduce the number of logic gates required to implement a function. The algebraic expression approach simplifies boolean functions by expressing them in a sum-of-products or product-of-sums form, which can then be minimized using Karnaugh maps or Quine-McCluskey algorithms. This process not only streamlines

Practical Applications and Modern Trends in Logic Gate Minimization

Logic gates form the fundamental building blocks of digital circuits, enabling computers and electronic devices to perform a myriad of functions through binary operations. Minimization techniques in logic gate design are critical for optimizing circuit performance, reducing power consumption, and enhancing integration density. Practical applications of these techniques span across various domains, from high-speed processors in supercomputers to the low-power microcontrollers in everyday appliances. In integrated circuits, minimized logic gates lead to a decrease in gate count and area, which directly translates to faster operation speeds and lower energy requirements. This is especially pertinent in the context of modern trends, where miniaturization and energy efficiency are paramount due to the increasing complexity of electronic systems and the need for sustainable technologies. Modern advancements in logic gate minimization leverage sophisticated algorithms, machine learning, and novel materials to push the boundaries of what’s achievable with current technology. The continuous refinement of these techniques not only contributes to more efficient electronics but also paves the way for new innovations in fields such as artificial intelligence, where complex neural networks rely heavily on the underlying logic gate infrastructure for their operation. As logic gate designs become more sophisticated, the integration of multiple functions into single gates and the use of advanced fabrication techniques further enhance the capabilities of digital circuits. These efforts ensure that logic gates remain at the forefront of technological progress, driving the evolution of electronic systems to meet the demands of an increasingly connected world.