Logic Gates Mastery: Enhancing FPGA Programming Efficiency

Logic gates are fundamental components of Field Programmable Gate Arrays (FPGAs), which are versati…….

Logic gates are fundamental components of Field Programmable Gate Arrays (FPGAs), which are versatile devices used for complex computations and data processing. These gates, including AND, OR, NOT, NAND, NOR, XOR, and XNOR types, can be programmed to execute a myriad of logical operations based on binary inputs, producing binary outputs. They are configured during the FPGA programming phase to meet specific digital logic requirements, with each gate type offering distinct functionalities that can be tailored for intricate digital systems design. The mapping of these gates onto FPGAs' configurable logic blocks (CLBs) and routing channels is essential for implementing desired functions, supporting rapid prototyping, dynamic reconfiguration, and making FPGAs highly adaptable for applications such as signal processing, communication networks, and more.

FPGAs' efficiency and performance are significantly influenced by the configuration of logic gates, which necessitate precise design to minimize delays and ensure reliability across different conditions. High-level descriptive languages like VHDL or Verilog are used to describe the behavior and interconnections of these gates, with FPGA development tools optimizing their performance. The adaptability of logic gates within FPGAs is particularly advantageous in environments that require real-time functionality changes or hardware adjustments on the fly. Advanced error correction mechanisms like ECCs are also integral to maintaining data integrity in FPGA architectures, requiring sophisticated logic gate configurations and constraint management to balance computational load with protection against faults and noise. Designers navigate through timing requirements, resource allocation, and interconnect management using tools like constraint programming and HDLs to ensure efficient and robust implementations suitable for complex applications. Overall, the role of logic gates in FPGA design is critical, as they enable high-performance, low-power, and scalable solutions in a variety of fields.

Explore the intricate world of Field Programmable Gate Arrays (FPGAs) through the lens of logic gate operations. This article delves into the fundamentals of logic gates within FPGA programming, elucidating their functions and significance in digital circuit design. We will traverse the types of logic gates pivotal to FPGA circuits, offering insights into their diverse roles. With a practical approach, we’ll guide you through designing with these gates, ensuring efficient implementation in FPGAs. Additionally, performance optimization techniques tailored for logic gate utilization are explored, enhancing your FPGA projects. Advanced discussions include error correction strategies and constraints specific to logic gate operations within FPGAs, equipping readers with comprehensive knowledge to navigate complex digital systems effectively. Join us as we unravel the logic behind FPGA programming.

- Fundamentals of Logic Gates in FPGA Programming

- Types of Logic Gates and Their Roles in FPGA Circuits

- Designing with Logic Gates: A Practical Approach to FPGA Implementation

- Optimizing Performance: Techniques for Efficient Logic Gate Utilization in FPGAs

- Advanced Topics in Logic Gate Operations within FPGAs, Including Error Correction and Constraints

Fundamentals of Logic Gates in FPGA Programming

Logic gates serve as the fundamental building blocks for digital circuits within Field Programmable Gate Arrays (FPGAs), enabling them to perform complex computations and data processing tasks. In FPGA programming, logic gates are configured to execute specific logical operations based on binary inputs, delivering binary outputs. These gates include the ubiquitous AND, OR, NOT, NAND, NOR, XOR, and XNOR types, each with distinct characteristics and functions that can be combined in various ways to construct digital systems. For instance, an AND gate produces a high output only when all its inputs are high, while an OR gate outputs high if at least one of its inputs is high. The NOT gate, on the other hand, inverts its input signal. FPGA programming involves mapping these logic gates onto the FPGA’s configurable logic blocks (CLBs) and routing channels to implement a desired digital logic function. This process allows for rapid prototyping and implementation of algorithms and systems that require dynamic reconfiguration, making FPGAs ideal for applications ranging from signal processing to high-speed communication networks.

The configuration of logic gates in an FPGA is a critical aspect of hardware design, as it directly impacts the efficiency and performance of the resulting circuit. Designers leverage high-level descriptive languages like VHDL or Verilog to describe the logic gates’ behavior and their interconnections. This high-level description is then synthesized by FPGA development tools into a configuration that optimizes resource utilization, minimizes delays, and ensures reliable operation under various conditions. The flexibility of FPGAs, coupled with the versatility of logic gates, allows for real-time modifications to the circuit’s functionality, which is invaluable in applications requiring adaptability or where hardware needs to be adjusted on the fly, such as in dynamic environments or when adapting to new protocols.

Types of Logic Gates and Their Roles in FPGA Circuits

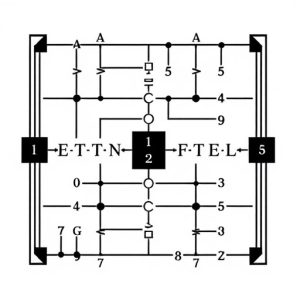

Logic gates serve as the fundamental building blocks for digital circuitry within Field-Programmable Gate Arrays (FPGAs), enabling them to perform a wide array of logical operations. In FPGA circuits, these gates can be configured and reconfigured to implement various functions, making them highly versatile components in digital design. The most common types of logic gates include AND, OR, NOT, XOR, XNOR, NAND, and NOR. Each type performs a distinct function: AND gates produce an output that is true only if all its inputs are true, while OR gates output true if at least one of their inputs is true. NOT gates invert the logic level of their single input, turning 1 into 0 and vice versa. XOR and XNOR gates compare their inputs and output true if the inputs are different (XOR) or the same (XNOR), respectively. NAND and NOR gates are dual versions of AND and OR gates, where the output is the negation of what the gate would normally produce.

In FPGA circuits, these logic gates can be interconnected in countless ways to create complex logic functions and sequences, such as counters, memory elements, and arithmetic units. The programmable nature of FPGAs allows designers to configure these gates dynamically, either at runtime or through a one-time programming event. This flexibility is particularly beneficial for prototyping new ideas, implementing algorithms efficiently, and even for hardware-in-the-loop testing, where the actual hardware can be tested with software that will run on it later. The ability to reconfigure these logic gates on-the-fly also makes FPGAs ideal for applications that require adaptability or for systems that must execute multiple functions without dedicated hardware for each one. Understanding the roles and capabilities of these logic gates is essential for anyone working with FPGA technology, as they form the basis of all digital computations within the FPGA.

Designing with Logic Gates: A Practical Approach to FPGA Implementation

Logic gates are fundamental building blocks in the realm of digital circuit design, particularly within Field Programmable Gate Arrays (FPGAs). When designing with logic gates for FPGA implementation, one must consider the efficient utilization of these gates to create complex functions without exceeding the hardware resources. The process begins with a high-level understanding of the desired functionality, which is then broken down into logical operations that can be executed by the FPGA’s configurable logic blocks (CLBs). Designers employ a top-down or bottom-up approach to synthesize these operations, translating behavioral descriptions into gates like AND, OR, XOR, NOT, and their more complex counterparts like flip-flops and registers.

The practical application of logic gates in FPGA design involves careful planning and optimization. Designers must map out the logic operations required for a specific task and select appropriate logic gate configurations to implement these functions. This requires an understanding of the FPGA’s architecture, including the interconnect structure that facilitates communication between different parts of the chip. By leveraging the inherent flexibility of FPGAs, designers can prototype and iterate designs rapidly, testing various configurations and optimizing performance and resource utilization. Tools like hardware description languages (HDLs), such as Verilog or VHDL, are instrumental in this process, allowing for a precise and unambiguous representation of the logic gates’ behavior. Through a combination of careful planning, efficient resource allocation, and iterative testing, designers can successfully implement complex digital systems using logic gates within FPGAs.

Optimizing Performance: Techniques for Efficient Logic Gate Utilization in FPGAs

In the realm of Field Programmable Gate Arrays (FPGAs), logic gates serve as the fundamental building blocks for digital circuit design. Efficient utilization of these logic gates is pivotal for optimizing performance within FPGGA-based systems. Designers can leverage several techniques to ensure that logic gate resources are allocated and utilized in a manner that maximizes speed and minimizes power consumption. One approach involves the careful selection of logic gate types, where low-latency gates such as LUTs (Look-Up Tables) or fast carry logic for adders are employed in critical paths. Another technique is to employ synthesis tools that optimize the placement and routing of logic gates, taking into account the FPGA’s architecture and interconnect structure. This ensures minimal delay and efficient signal propagation across the chip. Additionally, partitioning the design into smaller functional units can reduce the complexity of individual logic gate implementations and improve their performance characteristics. Furthermore, understanding the FPGA’s timing constraints and resource usage is essential for fine-tuning the logic gate architecture to achieve the desired balance between speed and resource utilization. By adopting these optimization strategies, designers can create highly efficient logic gate networks that enhance the overall functionality and responsiveness of their FPGA-based applications.

Advanced logic gate optimization in FPGAs often involves exploiting specific features unique to the hardware. For instance, leveraging hardware multipliers for arithmetic-heavy tasks or employing carry chain optimization for high-speed arithmetic operations can significantly reduce the computational burden on the FPGA. Moreover, using hierarchical logic design techniques allows for a more structured and maintainable approach to complex systems, ensuring that logic gates are not only used efficiently but also in a way that facilitates easier scaling and evolution of the system. Adept utilization of these advanced features requires an in-depth knowledge of both the FPGA architecture and the specific application’s requirements. By meticulously analyzing and optimizing the logic gate usage, designers can unlock the full potential of FPGAs to deliver high-performance, power-efficient, and scalable solutions.

Advanced Topics in Logic Gate Operations within FPGAs, Including Error Correction and Constraints

In the realm of Field-Programmable Gate Arrays (FPGAs), logic gates serve as fundamental building blocks for creating digital systems. Advanced topics in logic gate operations within FPGAs delve into the intricate mechanisms that enable these devices to execute complex tasks efficiently. One such advanced topic is error correction, which is critical in ensuring the integrity of data processing within FPGGAs. Error-correcting codes (ECCs) are integrated into FPGA architectures to protect against transient faults and noise corruption that can occur during signal propagation or from external environmental factors. These ECCs involve sophisticated logic gate configurations, such as Hamming codes for detecting and correcting single-bit errors or Reed-Solomon codes for handling multiple-bit errors. The implementation of these codes requires a careful balance between computational overhead and the robustness of protection they offer, a testament to the importance of logic gates in maintaining data fidelity within FPGA systems.

Constraints play a pivotal role in the design and operation of logic gates within FPGAs. Designers must consider timing constraints to ensure that signals propagate through the logic gates without violating the system’s clock frequency. Additionally, area and power consumption are significant factors; designers must optimize the placement and routing of logic gates to minimize silicon real estate and power dissipation, all while maintaining performance standards. Resource constraints, such as limited numbers of logic gate instances or interconnect resources, necessitate careful planning and sophisticated design methodologies. Constraint programming and hardware description languages (HDLs) are employed to define and manage these constraints, allowing for the creation of efficient and effective FPGA implementations that leverage the full potential of logic gates in complex applications.