Logic Gates & Noise Margin: Enhancing Digital Logic Resilience

Noise margin is a critical factor in the reliable operation of digital systems, ensuring logic gates…….

Noise margin is a critical factor in the reliable operation of digital systems, ensuring logic gates can accurately distinguish between '1' and '0'. Logic gates, as fundamental building blocks, maintain and boost noise margin, preserving signal integrity. Degradation caused by external interfering signals can lead to data corruption and system failures, emphasizing the importance of adequate noise margin. Techniques such as logic gate design with hysteresis, optimal power supply voltages, terminations, shielding, and advanced technologies lower noise levels, ensuring accurate data transfer. As digital systems miniaturize, minimizing noise becomes even more critical for performance and longevity, with ongoing research focusing on advanced materials, enhanced shielding, and sophisticated signal processing.

Noise margin, a critical concept in digital logic, refers to the difference between a signal’s level and the point at which it could be distorted or corrupted. Understanding this margin is crucial for ensuring reliable data transmission in digital systems, with noise resistance being paramount for logic gates.

Logic gates play a significant role in introducing or amplifying noise margin, impacting overall system performance. External interfering signals can disrupt these delicate balances, emphasizing the need for robust noise-resistant designs.

This article explores these dynamics, delving into techniques to fortify digital logic against noise and its real-world implications.

- Understanding Noise Margin: The Basic Concept

- How Logic Gates Contribute to Noise Margin

- Impact of External Interfering Signals

- Techniques to Enhance Noise Resistance in Digital Logic

- Real-world Applications and Future Trends

Understanding Noise Margin: The Basic Concept

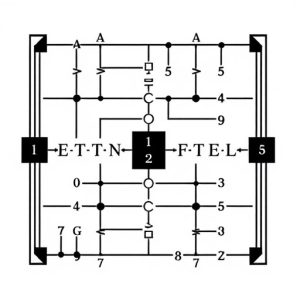

Noise margin, a fundamental concept in digital logic, refers to the difference between the logical level (typically represented by a voltage threshold) and the noise or interference present in the signal. In simple terms, it’s the clear space that allows logic gates to distinguish between a logical ‘1’ and a logical ‘0’. This distinction is crucial for ensuring reliable operation of digital systems, as even minor fluctuations due to noise can alter the interpretation of signals.

Logic gates, the building blocks of digital circuits, rely on precise voltage levels to encode and process information. A sufficient noise margin ensures that these gates can reliably discern between input states, minimizing errors caused by environmental interference or inherent circuit imperfections. Understanding and managing noise margin is therefore essential for designing robust digital logic systems capable of functioning accurately in various environments.

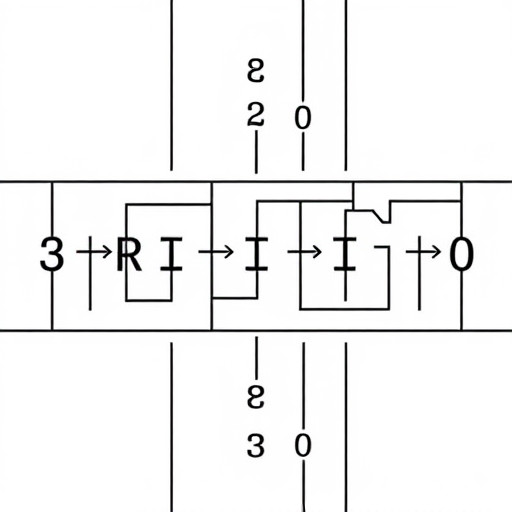

How Logic Gates Contribute to Noise Margin

Logic gates play a pivotal role in maintaining and enhancing noise margin within digital systems. These fundamental building blocks of digital logic are designed to process and transmit binary data with minimal distortion, ensuring signal integrity. Each logic gate acts as a filter, discerning between logical 0s and 1s, and amplifying the differences to counteract ambient noise and interference.

The design and functionality of logic gates directly impact their ability to contribute to noise margin. Advanced logic gates employ sophisticated techniques like differential signaling and ESD protection mechanisms to further reduce noise effects. By introducing these innovations, logic gates can not only preserve data accuracy but also expand the operational margins of digital circuits, making them more resilient in the face of environmental interference.

Impact of External Interfering Signals

External interfering signals can significantly impact the performance and reliability of digital logic circuits, particularly in the form of noise margin degradation. These signals, often originating from various sources like electrical appliances, radio transmissions, or even nearby digital circuits, introduce unwanted voltage fluctuations that can alter the intended logic levels within logic gates.

For instance, when a logic gate receives an input signal that is subject to interference, it may misinterpret the original logical state, leading to incorrect circuit behavior. This effect becomes more pronounced as the noise level increases, potentially causing data corruption, timing issues, and even system failures in extreme cases. Therefore, maintaining adequate noise margin is essential for ensuring the robust operation of digital logic gates and overall circuit integrity.

Techniques to Enhance Noise Resistance in Digital Logic

In digital logic, noise margin plays a pivotal role in ensuring the reliability and accuracy of signal transmission. To enhance noise resistance, several techniques are employed, primarily focusing on improving the strength of logical signals compared to interfering noise. One effective method is logic gate design, which includes implementing hysteresis in circuits to increase noise immunity. Hysteresis allows for a wider difference between the active and inactive states of gates, making it harder for noise to trigger spurious transitions.

Additionally, careful consideration of power supply voltage levels and signal integrity is vital. Using cleaner, more stable power sources and employing techniques like terminations and shielding can significantly reduce noise coupling. Logic gates designed with advanced technologies that offer lower noise floor and improved signal processing capabilities further contribute to enhanced noise resistance in digital systems.

Real-world Applications and Future Trends

In real-world applications, noise margin plays a pivotal role in ensuring the reliability and performance of digital logic circuits, particularly in the realm of logic gates. By providing a buffer against external interference and internal fluctuations, it allows for clearer signal interpretation, leading to more accurate computations. This is especially critical in high-speed digital systems where even minute noise can disrupt operations, impacting devices from simple memory chips to complex microprocessors.

Looking ahead at future trends, advancements in technology are expected to further refine the concept of noise margin. As digital systems continue to shrink and become more compact, minimizing noise becomes increasingly essential for maintaining efficiency. Researchers are exploring innovative techniques such as advanced materials, enhanced shielding, and sophisticated signal processing algorithms to combat noise at its source. These efforts promise not only improved performance but also extended operational lifespans for future generations of logic gates and digital devices.