Logic Gates & Circuit Timing: Measuring Propagation Delays, Clock Synchronization

Logic gates are fundamental to digital electronics, processing and controlling electrical signals th…….

Logic gates are fundamental to digital electronics, processing and controlling electrical signals through logical operations like AND, OR, NOT, and NAND. Timing analysis in logic circuits is crucial for optimization, focusing on gate interactions, propagation delays, and architectural complexity. Factors such as transistor speed, supply voltage, and temperature also impact delay. Precise measurement techniques, along with simulation software, aid engineers in optimizing logic gate architectures for faster performance. Clock synchronization, enabled by tools like phase-locked loops (PLLs), ensures data processing efficiency and prevents race conditions. Advanced simulators and formal methods provide a comprehensive view of signal delays, enabling early identification of bottlenecks and informed circuit design decisions.

In the intricate world of digital design, understanding timing analysis in logic circuits is paramount. Logic gates, these fundamental building blocks, orchestrate signal flow and determine circuit performance. This article delves into the core concepts, exploring how logic gates influence propagation delay. We dissect various factors affecting circuit timing, unveiling techniques for precise measurement and analysis. Additionally, we scrutinize clock synchronization’s profound impact on overall efficiency. With advanced tools and methods, readers will gain comprehensive insights into navigating the intricate landscape of logic circuit timing.

- Understanding Logic Gates and Their Role in Circuit Timing

- Factors Affecting Propagation Delay in Logic Circuits

- Techniques for Measuring and Analyzing Timing Parameters

- Clock Synchronization and Its Impact on Circuit Performance

- Advanced Tools and Methods for Comprehensive Timing Analysis

Understanding Logic Gates and Their Role in Circuit Timing

Logic gates are fundamental building blocks in digital electronics, acting as the gatekeepers of circuit timing and functionality. Each gate performs specific logical operations, such as AND, OR, NOT, and NAND, by manipulating the flow of electrical signals based on defined inputs. Their primary role is to process and transmit information within a circuit, ensuring that signals are timed and controlled precisely.

The timing analysis of logic circuits heavily relies on understanding how these gates interact. The propagation delay, or the time it takes for an output to change in response to an input, varies between different logic gates. By examining these delays, engineers can predict and optimize circuit performance. Efficiently designed logic gates ensure that signals travel through a circuit without unnecessary bottlenecks, thereby enhancing overall timing accuracy and circuit speed.

Factors Affecting Propagation Delay in Logic Circuits

The propagation delay in logic circuits, which refers to the time taken for a signal to travel from one logic gate to another, is influenced by several factors. One primary factor is the complexity and architecture of the circuit itself. As circuits become more intricate with an increased number of logic gates and interconnections, signal propagation becomes slower due to the cumulative effect of each gate’s processing time. This delay can be further compounded by factors like the speed of the transistors within the gates, which are determined by their technology node (e.g., 7nm, 10nm).

Additionally, supply voltage and temperature play significant roles in propagation delay. A lower supply voltage can lead to slower switching times for transistors, thereby increasing the overall circuit delay. Similarly, higher temperatures can cause transistors to operate less efficiently, resulting in longer signal propagation times. These environmental factors must be carefully considered during circuit design to ensure optimal performance across a range of operating conditions.

Techniques for Measuring and Analyzing Timing Parameters

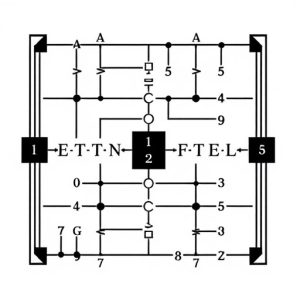

In the realm of logic circuits, accurately measuring and analyzing timing parameters is paramount for ensuring optimal performance and functionality. Techniques such as edge detection and pulse width measurement play a pivotal role in this process. Edge detection involves identifying the rising and falling edges of signals within logic gates, providing crucial insights into signal transition times. This method is essential for gauging propagation delays, which can significantly impact overall circuit speed.

Pulse width measurement, on the other hand, focuses on assessing the duration of active signal levels. By meticulously timing the widths of pulses generated by logic gates, engineers can pinpoint potential bottlenecks and fine-tune circuit timings. These techniques, combined with advanced simulation tools, enable thorough analysis of complex circuits, ultimately driving the design of faster, more efficient logic gate architectures.

Clock Synchronization and Its Impact on Circuit Performance

In digital logic circuits, clock synchronization plays a pivotal role in ensuring efficient and accurate data processing. The clock signal acts as a metronome, coordinating the operations of various logic gates by providing a common timing reference. This synchronization is critical for maintaining the integrity of data transmission and preventing race conditions within the circuit. Each logic gate is designed to respond at specific times relative to the clock edge (rising or falling), enabling serial data flow and concurrent processing in complex circuits.

Effective clock synchronization directly impacts circuit performance, affecting factors such as speed, latency, and power consumption. Advanced techniques like phase-locked loops (PLLs) are employed to generate precise clock signals, allowing for higher operating frequencies. Accurate timing analysis, including edge detection and propagation delay calculations, is essential to optimize the circuit design in terms of both speed and energy efficiency. By meticulously managing clock synchronization, engineers can unlock the full potential of logic gates, resulting in faster computation and enhanced overall circuit performance.

Advanced Tools and Methods for Comprehensive Timing Analysis

In the realm of logic circuit design, advanced tools and methods have emerged as indispensable assets for achieving precise timing analysis. These sophisticated techniques go beyond basic simulation to offer a comprehensive view of signal propagation delays, setup times, and hold requirements within complex digital systems. By employing high-fidelity simulators with built-in timing verification features, engineers can simulate not just the behavior of individual logic gates but also the interconnections between them, revealing potential timing bottlenecks early in the design process.

Moreover, formal methods such as temporal logic and abstract interpretation provide rigorous approaches to timing analysis. Temporal logic allows for the expression of timing constraints as first-order properties, enabling automated verification against these constraints. Abstract interpretation, on the other hand, offers a methodical way to approximate and reason about timing behavior at various levels of abstraction. When combined, these advanced tools and methods enable designers to make informed decisions, optimize circuit performance, and ensure reliable operation in high-speed digital systems, all without succumbing to the complexities of manual analysis.