Strengthening Digital Systems: Fault Tolerance in Logic Gates

In the digital world, logic gate networks are essential for efficient data processing, with fault to…….

In the digital world, logic gate networks are essential for efficient data processing, with fault tolerance as a top priority to ensure system reliability. By designing robust mechanisms, engineers create resilient logic gates that enhance integrity, accuracy, and uptime. Logic gates, such as AND, OR, and NOT, form complex networks like FPGAs, but they face failures due to component degradation or environmental stressors. Redundancy and error detection/correction codes (EDAC) are key techniques to build fault-tolerant logic gate networks, ensuring operational stability in critical applications like avionics and financial systems. Understanding these gates is crucial for optimizing data flow within electronic devices in today's digital era.

Fault tolerance is a critical aspect of modern digital systems, particularly in complex networks reliant on logic gates. This article delves into the essential concept of fault tolerance within logic gate networks, exploring why robustness is paramount for reliable operation. We’ll examine the foundational role of logic gates in digital architectures, common failures that can occur, and advanced techniques for constructing fault-tolerant systems. By understanding these elements, we can appreciate the practical applications of fault tolerance in contemporary computer design.

- Understanding Fault Tolerance: The Need for Robustness in Logic Gate Networks

- Introduction to Logic Gates and Their Role in Digital Systems

- Common Failures in Logic Gate Circuits and Their Impact

- Techniques for Building Fault-Tolerant Logic Gate Networks

- Practical Applications of Fault Tolerance in Modern Computer Architecture

Understanding Fault Tolerance: The Need for Robustness in Logic Gate Networks

In the intricate world of digital systems, logic gate networks form the backbone of data processing and computation. These networks, composed of interconnected logic gates, are responsible for executing complex operations with precision and speed. However, the quest for unparalleled performance must be balanced against the ever-present threat of faults—whether due to hardware malfunctions, power surges, or environmental factors. This is where fault tolerance steps in as a critical component, ensuring that even in the face of adversity, the logic gate network maintains its integrity and reliability.

Understanding fault tolerance involves recognizing that digital systems are susceptible to errors, and designing networks capable of detecting, isolating, and recovering from these faults without compromising overall performance. This robustness is essential for maintaining data accuracy, system uptime, and ensuring the seamless execution of tasks dependent on logic gate networks. By implementing fault-tolerant mechanisms, engineers can build more reliable systems, catering to the demanding needs of modern computing and data-intensive applications.

Introduction to Logic Gates and Their Role in Digital Systems

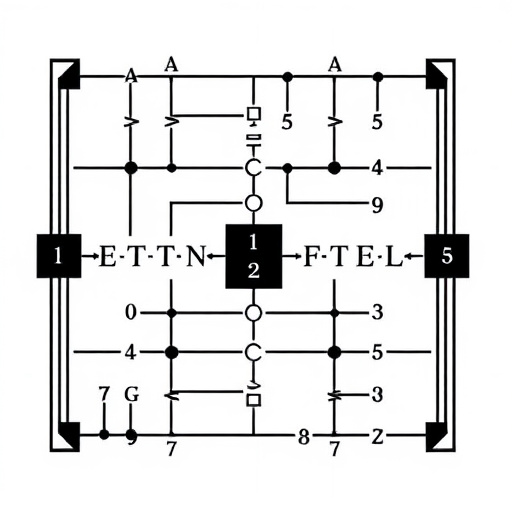

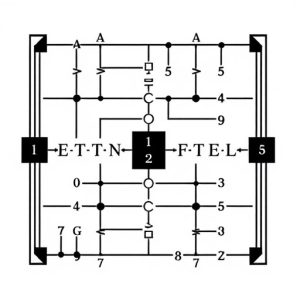

Logic gates are fundamental building blocks in digital systems, acting as the cornerstones of complex computing networks. These simple electronic circuits perform basic logical operations, such as AND, OR, and NOT, by controlling the flow of binary data. Each logic gate takes one or more inputs, processes them according to a specific logical function, and produces an output based on predefined rules.

In digital systems, logic gates are interconnected to form larger networks known as logic gate arrays or field-programmable gate arrays (FPGAs). This hierarchical structure enables the implementation of intricate algorithms and computational tasks. The role of fault tolerance in these networks is paramount, ensuring that even with component failures, the overall system remains operational and provides accurate results. By employing redundancy, error detection mechanisms, and robust design principles, modern digital systems can maintain their integrity and reliability.

Common Failures in Logic Gate Circuits and Their Impact

Logic gate circuits, despite their fundamental role in digital systems, are susceptible to various failures that can disrupt their functionality and performance. Common issues include component degradation, aging, manufacturing defects, and environmental factors like temperature variations and power fluctuations. These failures can manifest as logic level shifts, timing discrepancies, or even complete circuit failure.

The impact of these failures is significant. They can lead to data corruption, system crashes, and reduced reliability, especially in critical applications like avionics, medical devices, and financial systems. Understanding and mitigating these potential problems are crucial for designing robust logic gate networks that ensure operational continuity and maintain the integrity of processed information.

Techniques for Building Fault-Tolerant Logic Gate Networks

Building fault-tolerant logic gate networks requires implementing robust techniques to ensure the reliability and continuity of digital systems. One effective approach is redundancy. By creating multiple paths for signal flow, even if one path fails, backup pathways can continue processing, maintaining system functionality. This redundancy can be achieved through parallel circuits or diverse routing strategies.

Another powerful technique involves error detection and correction codes (EDAC). These codes are designed to identify and rectify errors within data transmission. By incorporating EDAC into logic gate networks, any bit flipping or corruption during transmission can be detected and corrected, minimizing the impact of faults on overall system performance. This ensures that logic gates operate with enhanced accuracy and stability, even in challenging environments.

Practical Applications of Fault Tolerance in Modern Computer Architecture