Optimizing Logic Gate Performance Through Effective Timing Analysis

Timing analysis in digital circuit design is essential for optimizing the performance of logic gate…….

Timing analysis in digital circuit design is essential for optimizing the performance of logic gates, ensuring that high-speed digital circuits function correctly and efficiently. This critical process evaluates key parameters like setup time, hold time, propagation delay, and transition delay to predict and manage circuit behavior under various operational conditions. Designers must manipulate these timing characteristics to prevent issues such as race conditions or data corruption, guaranteeing the longevity and reliability of electronic devices across diverse sectors. Mastery of timing analysis is imperative for high-speed digital circuit design, ensuring that circuits meet performance benchmarks and operate optimally without sacrificing power efficiency. Through a combination of simulation and modeling techniques, designers can create detailed virtual prototypes to predict signal integrity issues before physical realization, enhancing the predictability and reliability of logic gates in complex digital systems. Keywords: logic gates, timing analysis, signal propagation, performance optimization, reliability, simulation, modeling, high-speed circuits, and predictive analytics.

delve into the critical domain of logic gate performance, this article illuminates the pivotal role of timing analysis in ensuring the efficiency and reliability of digital circuits. Exploring fundamental concepts through advanced methodologies, it outlines the key components and metrics that underpin effective timing evaluation. From simulation and modeling to overcoming practical challenges, the piece provides a comprehensive guide to mastering timing analysis techniques and best practices. Real-world case studies highlight their application in logic circuit design, ensuring readers are well-equipped to navigate the intricacies of this essential aspect of modern electronic systems.

- Understanding Timing Analysis in the Context of Logic Gates

- Key Components and Metrics in Timing Analysis for Digital Circuits

- Methodologies for Timing Analysis: Simulation and Modeling Approaches

- Overcoming Challenges in Timing Analysis: Techniques and Best Practices

- Case Studies: Real-World Applications of Timing Analysis in Logic Circuit Design

Understanding Timing Analysis in the Context of Logic Gates

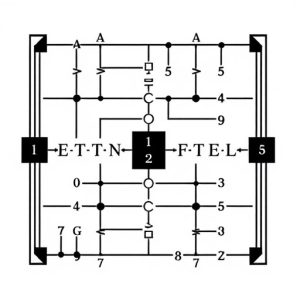

In the realm of digital circuit design, timing analysis is a critical aspect that ensures signals propagate through logic gates within the specified time constraints. This process involves evaluating the timing characteristics of each gate to predict the performance of the circuit under various conditions. Logic gates, the fundamental building blocks of digital circuits, consist of transistors configured to perform logical operations such as AND, OR, NOT, XOR, and so on. The timing analysis of these gates is pivotal in determining the overall speed and reliability of a digital system. It encompasses various parameters including setup time, hold time, propagation delay, and transition delay. Setup time refers to the minimum amount of time a input signal should be stable before the logic gate changes state, while hold time is the time after a input change during which the input signal should remain stable to avoid incorrect operation. Propagation delay measures the time taken for a change at the input to reflect at the output, and transition delay pertains to the time required for a stable output following an input transition. By understanding these characteristics, designers can optimize the timing of signals to prevent race conditions, glitches, or other timing violations that could lead to circuit malfunction or data corruption. Consequently, mastery of timing analysis in the context of logic gates is essential for high-speed digital circuit design and the reliable functioning of electronic devices across various applications.

Key Components and Metrics in Timing Analysis for Digital Circuits

In the realm of digital circuit design, timing analysis is a critical process that ensures the logical elements operate within their specified speed requirements to meet the desired performance criteria. Central to this process are logic gates, which are the fundamental building blocks of all digital circuits. These gates include AND, OR, NOT, XOR, and various other types, each with characteristic delay times. Timing analysis involves evaluating the propagation delays through these gates to ascertain that data flows through the circuit swiftly enough to satisfy the timing constraints set for the system’s functionality. The key components in this evaluation include the setup and hold times of flip-flops, which dictate the time intervals between clock pulses and data transitions to avoid erroneous state interpretations. Additionally, the critical path delay, which is the longest path through a combinational logic network that affects the overall timing of the circuit, is a pivotal metric. Other metrics such as timing slack, path delay, and clock-to-Q (CK-to-Q) time are also crucial in assessing the timing behavior of digital circuits. Understanding these components and metrics allows designers to optimize the logic gates’ arrangement and configuration for faster operation or to scale down power consumption without compromising on performance. This optimization is essential for the design’s reliability, especially as technology advances towards smaller feature sizes and higher frequencies. By meticulously analyzing the timing characteristics of each logic gate within the circuit, designers can predict and prevent potential timing violations before physical implementation, thereby ensuring that the digital circuit functions correctly under its intended conditions.

Methodologies for Timing Analysis: Simulation and Modeling Approaches

In the domain of digital circuit design, timing analysis is a critical process that ensures the signals within logic circuits operate within their specified time constraints to function correctly. This is particularly pertinent in high-speed environments where the propagation delay through logic gates becomes a limiting factor. Methodologies for timing analysis encompass both simulation and modeling approaches, each offering unique advantages and applications. Simulation methodologies employ computer models to predict the behavior of logic circuits under various conditions. These simulations can be static, analyzing a single set of conditions, or dynamic, considering multiple scenarios and their potential impacts on signal propagation. By accurately modeling logic gates, engineers can simulate the circuit’s response to different inputs and clock frequencies, identifying timing violations before physical implementation. This predictive capability is invaluable for optimizing performance and reliability.

Modeling approaches go beyond mere simulation by creating detailed representations of the logic gates and their interactions within the circuit. These models can be used to construct virtual prototypes that closely mimic real-world behavior. The use of advanced modeling techniques, such as timing analysis algorithms that incorporate statistical variations in device characteristics, allows for a more comprehensive understanding of signal integrity under different operational conditions. This level of granularity is essential for complex logic circuits where timing margins are razor-thin and any delay can lead to malfunction or data corruption. By leveraging both simulation and detailed modeling, designers can effectively predict and manage the timing characteristics of logic gates, ensuring that the circuit’s performance meets the stringent demands of modern applications.

Overcoming Challenges in Timing Analysis: Techniques and Best Practices

In the realm of digital circuit design, timing analysis is a critical aspect that ensures signals propagate through logic gates within specified time constraints to meet system performance requirements. One of the primary challenges in timing analysis is dealing with the increasing complexity and speed of modern circuits, which necessitates precise timing models and sophisticated simulation tools. To address these challenges, designers employ a variety of techniques. Firstly, they utilize static timing analysis (STA) to predict the timing behavior of the circuit under various conditions. This involves establishing timing paths that represent the critical paths in the circuit, where delays through logic gates are evaluated against the clock period or setup and hold times required by flip-flops.

Another technique used to overcome timing issues is the application of dynamic timing analysis, which takes into account variations in signal integrity, process, voltage, and temperature (PVT) conditions, and manufacturing variability. Designers also leverage advanced simulation software that can model multiple corners of operation, providing a more comprehensive understanding of how the circuit will perform under different scenarios. Best practices in logic circuit design further enhance timing predictability. These include the careful placement of logic gates to minimize interconnect delays, the use of timing closure methodologies, and the implementation of design rules checks (DRC) and layout versus schematic (LVS) comparisons to ensure the physical layout aligns with the logical design. Additionally, designers often iterate designs using a bottom-up approach, starting with the logic gates and progressively building up to larger blocks, which helps in identifying potential timing violations early in the design process. By combining these techniques and best practices, designers can effectively navigate the complexities of timing analysis and produce reliable logic circuits that meet the stringent timing requirements of modern electronic systems.

Case Studies: Real-World Applications of Timing Analysis in Logic Circuit Design

In the realm of digital circuit design, timing analysis plays a pivotal role in ensuring that electronic systems perform as intended. The precision of logic gates, which are the fundamental building blocks of digital circuits, is directly influenced by timing analysis. For instance, in high-speed memory designs, such as DRAM or SRAM, timing analysis is crucial for the synchronization between memory access and data processing operations. This synchronization is achieved through careful design considerations that account for propagation delays, setup, and hold times at the logic gates involved in memory control circuitry.

Moreover, in applications requiring high-speed data processing, like high-frequency clock generators or complex signal conditioning circuits in telecommunication systems, timing analysis is integral to the design process. Engineers employ advanced tools and methodologies to simulate and analyze the timing characteristics of logic gates under various conditions. These simulations enable designers to predict performance and optimize the circuit for the fastest possible operation without compromising data integrity. For example, in designing a high-speed serial link, timing analysis helps in setting up the correct timing margins at the logic gates to prevent data errors due to skew and jitter. The real-world applications of timing analysis in logic circuit design underscore its importance in achieving predictable and reliable performance across a wide range of digital systems.