Mastering Timing Analysis in Logic Circuits: A Guide to Logic Gates and Precision Timing

Logic gates serve as the building blocks of digital circuits, performing fundamental logical operati…….

Logic gates serve as the building blocks of digital circuits, performing fundamental logical operations that dictate more complex system behaviors. These gates, which include AND, OR, NOT, XOR, and others, function according to Boolean algebra principles for reliable performance. Timing analysis is a critical aspect of designing these circuits, focusing on synchronization and optimization of timing parameters like setup and hold times, signal propagation delays, and combinational logic path delays to ensure high-speed operation and prevent malfunctions. As technology advances and logic circuits become more miniaturized, precise timing becomes increasingly challenging yet essential for maintaining circuit integrity. Static Timing Analysis (STA) is a key tool used to predict circuit behavior, considering both static conditions for accurate predictions and dynamic conditions for real-world precision. This process involves examining the timing of signals as they pass through logic gates, ensuring that circuits meet their performance standards. Accurate delay modeling, identifying critical paths, and adhering to a timing budget are all part of this analysis, which is crucial for achieving timing closure and enhancing the robustness and reliability of digital logic circuits across various applications, including consumer electronics and advanced computing systems. STA's role in electronic design automation is indispensable for guaranteeing that logic circuits operate within their prescribed time constraints, ensuring consistent performance under diverse environmental and operational conditions.

In the realm of digital electronics, the precise synchronization of logic gates is pivotal for optimal performance. This article delves into the critical aspect of timing analysis within logic circuits, a discipline essential for ensuring that digital systems operate efficiently and reliably. We will explore the fundamentals of logic gates, the importance of timing precision in digital circuits, and key concepts that underpin timing analysis. Furthermore, we will examine established methodologies, including Static Timing Analysis (STA) and Dynamic Timing Analysis (DTA), to manage the complexities of clock domains and synchronization. The intricacies of identifying and analyzing timing paths, critical path determination, and effective strategies for overcoming timing violations through delay calibration and design-for-timing (DFT) approaches will be discussed. Advanced tools for logic circuit analysis, such as simulation software and timing analyzers, are also in the spotlight. Through case studies that highlight real-world applications, we will navigate emerging trends and future directions in this dynamic field. Finally, we will conclude with best practices for robust timing analysis techniques to ensure reliability, particularly in high-speed and complex logic circuits, and address the interplay between timing analysis and fault tolerance.

- Fundamentals of Logic Gates and Timing Analysis

- The Importance of Precise Timing in Digital Circuits

- Key Concepts in Timing Analysis for Logic Circuits

- Timing Analysis Methodologies

- – Static Timing Analysis (STA)

Fundamentals of Logic Gates and Timing Analysis

Logic gates serve as the basic building blocks of digital circuits, performing fundamental logical functions that ultimately dictate the behavior and operation of more complex systems. These elementary units can execute operations such as AND, OR, NOT, XOR, and others, manipulating binary inputs to produce a single binary output. The design and function of logic gates are governed by Boolean algebra, ensuring that they operate in a predictable and reliable manner. Understanding the interplay between different logic gates is crucial for constructing digital circuits with desired functionalities.

Timing analysis in the context of logic circuits is a critical process that ensures the synchronization and optimal performance of these circuits. This analysis involves evaluating the timing characteristics and constraints of the circuit, such as setup and hold times, to prevent race conditions or metastability issues. It encompasses a detailed examination of signal propagation delay, clock period, and combinational logic path delays. By conducting thorough timing analysis, engineers can predict the performance of the circuit under various conditions, leading to reliable and high-speed digital systems. This is particularly important as logic circuits continue to shrink in size and increase in speed, making timing violations more likely and their impact more significant. The process of timing analysis is iterative and involves both static timing analysis, which uses conservative estimates, and dynamic timing analysis, which accounts for actual run-time conditions. This ensures that the digital circuit operates within its specified performance parameters and meets the design intent.

The Importance of Precise Timing in Digital Circuits

In the realm of digital circuits, precise timing is paramount for ensuring that logic gates function as intended and that data flows accurately through complex systems. The behavior of logic gates, which form the building blocks of digital circuits, relies on well-defined timing intervals to transition between states. These intervals dictate how signals propagate, how data is processed, and how devices synchronize with one another. Any deviation from these precise timings can lead to errors, glitches, or even system failure, emphasizing the critical nature of timing analysis in circuit design. Designers must account for factors such as signal delay, setup and hold times, and propagation delays to maintain a coherent clock signal and data integrity across all components. This meticulous attention to timing allows digital circuits to operate at high speeds and with high reliability, which is essential for applications ranging from consumer electronics to high-performance computing systems. The precision of timing in digital circuits not only affects the correctness of computations but also impacts the energy efficiency and performance of these systems, making it an indispensable aspect of logic circuit design and analysis.

Key Concepts in Timing Analysis for Logic Circuits

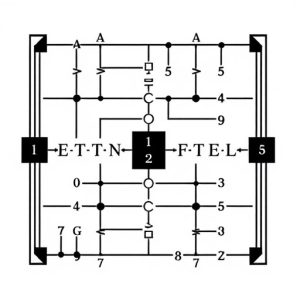

In the realm of digital circuit design, timing analysis is a critical process that ensures signals propagate through logic gates within specified time constraints to meet performance and functional requirements. This process involves evaluating the timing characteristics of each logic gate within a circuit to ascertain that the signal transitions occur at the correct times relative to the clock or other critical events. Delay modeling of logic gates is fundamental; it quantifies the delay from input to output for each gate, considering factors such as load capacitance and operating frequency. This data informs the timing budget, which sets the boundaries for acceptable signal delays throughout the circuit.

The timing analysis also encompasses the study of critical paths, which are the longest sequences of logic gates through which a signal must pass without incurring excessive delay. Identifying these paths is essential for optimizing the overall timing performance of the circuit. The concept of timing closure, achieved when all critical paths meet their respective timing specifications, is paramount. Tools and methodologies such as static timing analysis (STA) are employed to predict the behavior of signals and to verify that the design meets its timing requirements before physical implementation. By rigorously analyzing the performance of logic gates at various points in the design cycle, designers can preemptively address potential timing issues, ensuring robust and reliable operation of the digital circuit.

Timing Analysis Methodologies

In the realm of electronic design automation, timing analysis methodologies play a pivotal role in ensuring that logic circuits function optimally within their specified time constraints. These methodologies are critical for verifying that digital circuits composed of logic gates meet the timing requirements set forth by their designed purpose. Timing analysis involves evaluating the circuit’s performance against a series of clock cycles to ensure signals propagate through logic gates without exceeding the allowable delays. This is achieved through various methodologies, including static timing analysis, which checks the timing constraints based on worst-case conditions, and dynamic timing analysis, which considers the variations in signal values over time, such as those due to temperature changes or process variations.

Static timing analysis is a foundational methodology that examines the circuit’s critical paths, identifying any potential bottlenecks where signal delays could violate timing constraints. It employs a deterministic approach by using worst-case estimates for all variables, including gate delays and signal propagation times through logic gates. On the other hand, dynamic timing analysis goes beyond static analysis by incorporating statistical models to account for transient behavior in the circuit. This methodology simulates a range of scenarios, including various operating conditions and signal loadings, to predict the likelihood of timing violations over time. Both approaches are essential for designing robust logic circuits that operate reliably across different environmental conditions and manufacturing processes, ensuring the integrity and performance of electronic systems.

– Static Timing Analysis (STA)

In the realm of digital circuit design, Static Timing Analysis (STA) is a critical component in ensuring that logic circuits operate within specified timing constraints. STA evaluates the timing characteristics of a circuit under all possible conditions to guarantee that signals propagate through logic gates at an appropriate speed, thus preventing race conditions and potential failures. By analyzing the timing paths between various logic gates, designers can identify bottlenecks or potential delays that could cause the circuit to violate timing requirements. This process involves calculating the critical path delay, which is the sum of the delays through all the logic gates along the longest path from the input to the output within the circuit. The precision of STA allows for the optimization of gate-level designs before physical implementation, saving time and resources by reducing the likelihood of timing issues in subsequent phases of development.

Furthermore, STA is an indispensable tool in the design process as it incorporates both the static characteristics of logic gates and the dynamic nature of signal propagation. It accounts for various factors such as gate delays, load capacitances, and setup and hold times. By doing so, designers can anticipate how the circuit will perform under real-world conditions, long before the physical silicon is fabricated. This proactive approach to timing verification not only enhances the reliability of the digital circuit but also streamlines the design cycle by pinpointing potential issues early on. As a result, STA plays a pivotal role in maintaining the integrity and functionality of complex logic circuits across various applications where timing is paramount.