Logic Gates: Unlocking Semiconductor Design’s Building Blocks and Future

Logic gates, like AND, OR, and NOT, are essential building blocks in semiconductor design, enabling…….

Logic gates, like AND, OR, and NOT, are essential building blocks in semiconductor design, enabling engineers to create complex digital systems from calculators to data processors. Gate arrays, including standard cell arrays and look-up tables (LUTs), offer versatility and customization for diverse applications. Designing these arrays requires balancing logic gate selection with circuit performance optimization and physical implementation considerations. Gate arrays enhance performance and optimize space in electronic devices, but face design complexity and thermal management challenges. Future advancements aim to boost performance and integration through novel materials like heterojuncture transistors and 3D stacking, as well as AI-driven data processing for applications in high-performance computing, robotics, and smart cities.

“Gate arrays, a pivotal component in semiconductor design, are built upon the fundamental blocks of logic gates. This article explores these intricate structures, delving into the various types and their diverse applications. From understanding basic logic gates to navigating complex design considerations, we uncover the advantages and challenges within the semiconductor realm. Furthermore, we gaze into future trends, highlighting advancements that promise to revolutionize technology.”

- Understanding Logic Gates: The Building Blocks

- Types of Gate Arrays and Their Applications

- Design Considerations for Gate Arrays

- Advantages and Challenges in Semiconductor Design

- Future Trends in Gate Array Technology

Understanding Logic Gates: The Building Blocks

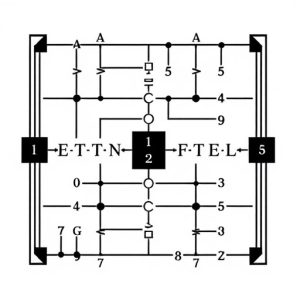

Logic gates are the fundamental building blocks in semiconductor design, acting as the intricate switches that process and manipulate digital information. These basic units, often consisting of AND, OR, and NOT functions, form the core of complex integrated circuits (ICs). By combining these logic gates, designers can create an array of digital systems capable of performing various tasks, from simple calculations to advanced data processing.

Each logic gate operates on binary inputs, producing a single output based on predefined logical rules. For instance, an AND gate requires both inputs to be high for activation, symbolizing the conjunction of two conditions. Conversely, an OR gate triggers when at least one input is active, representing alternative possibilities. Understanding these basic principles allows engineers to construct intricate logic arrays, enabling the creation of versatile and efficient semiconductor designs.

Types of Gate Arrays and Their Applications

Gate arrays, a fundamental building block in semiconductor design, encompass diverse types tailored for specific applications. Among them, standard cell arrays and look-up tables (LUTs) are prevalent. Standard cell arrays consist of pre-designed logic gates like AND, OR, and NOT, making them versatile for implementing complex digital circuits with varied functionality. These arrays find extensive use in microprocessors, memory controllers, and other system-on-a-chip (SoC) designs where efficient logic implementation and high performance are paramount.

In contrast, LUTs offer a more specialized approach by storing a table of pre-computed outputs for specific inputs. This lookup mechanism simplifies complex Boolean functions, enhancing design efficiency. LUTs are particularly advantageous in applications demanding lower power consumption and faster operation, such as FPGAs (Field Programmable Gate Arrays) used in data center networking, high-performance computing, and AI acceleration. Their flexibility allows designers to customize hardware for specific tasks, making them a popular choice in modern digital electronics.

Design Considerations for Gate Arrays

When designing gate arrays, several key considerations come into play. Firstly, the choice of logic gates and their arrangement is paramount. Different types of logic gates, such as AND, OR, NOT, and NAND, offer varied functionality, and their strategic placement can significantly impact the efficiency and performance of the circuit. Designers must balance signal integrity, power consumption, and speed when selecting gate configurations.

Another crucial aspect is the physical implementation. This includes considerations like interconnect design, where efficient routing strategies are essential to maintain signal integrity and minimize delays. The layout should also account for noise reduction techniques, power distribution, and heat dissipation to ensure reliable operation. Additionally, designing for scalability and modularity allows for easier updates and modifications in future iterations.

Advantages and Challenges in Semiconductor Design

In semiconductor design, gate arrays offer a multitude of advantages that drive innovation in electronics. One of the key benefits is their ability to enhance performance through high-speed processing and efficient logic operations facilitated by logic gates. These circuits form the backbone of digital systems, enabling complex calculations and data manipulation at remarkable speeds. Gate arrays also optimize space, reducing the need for extensive wiring and components, thereby minimizing the physical footprint of electronic devices.

Despite these advantages, challenges remain in semiconductor design. Design complexity is a significant hurdle, as creating intricate logic gates and interconnecting them without errors requires meticulous planning and sophisticated software tools. Furthermore, thermal management poses a challenge due to the high density of components in gate arrays, leading to increased power dissipation and potential overheating issues. Overcoming these challenges involves continuous advancements in design methodologies, materials science, and thermal cooling technologies to ensure the reliable and efficient operation of semiconductor devices.

Future Trends in Gate Array Technology

The future of gate array technology looks promising, with a focus on enhancing performance and integration. Advancements in logic gates, the fundamental building blocks of semiconductors, will continue to drive innovation. Researchers are exploring new materials and architectures, such as heterojuncture transistors and 3D stacking, to achieve higher speeds, lower power consumption, and increased density. These breakthroughs promise to revolutionize various industries, from high-performance computing to edge devices.

Additionally, the integration of artificial intelligence (AI) and machine learning algorithms into gate arrays is on the rise. This fusion of hardware and software enables more efficient and intelligent data processing, opening doors for applications in autonomous systems, advanced robotics, and smart cities. As technology evolves, we can expect even more sophisticated gate array designs that cater to the burgeoning demand for faster, smarter, and more energy-efficient semiconductor solutions.