Demystifying Demultiplexers: Logic Gate Foundations for Digital System Design

1:2^n demultiplexers are essential components in digital systems, directing input signals to specifi…….

1:2^n demultiplexers are essential components in digital systems, directing input signals to specific outputs based on binary codes. They utilize logic gates such as AND, OR, and sometimes multiplexer (MUX) gates to interpret addresses and route signals efficiently. These devices enable precise control over data flow, are scalable for various applications, and are foundational in memory addressing, network routing, and managing complex digital systems. Mastery of logic gates is crucial for designing demultiplexers that handle data streams with accuracy and speed, and their integration is vital for the efficient operation of electronic circuits across a range of digital technologies.

In the intricate fabric of digital systems, demultiplexers serve as critical components that enable the selective routing of data signals. This article delves into the essential role of demultiplexers within these systems, exploring their function, design, and applications through a lens focused on logic gates. Beginning with a foundational understanding of demultiplexers and their place in digital signal processing, we’ll navigate through the various types of demultiplexers, from simple 1:1 to complex 1:2^n multiplexers. We’ll dissect how these devices operate and function at the circuit level, using logic gates as building blocks. Subsequent sections will cover practical applications, performance analysis, and the nuanced differences between demultiplexers and their counterparts, multiplexers. Additionally, we’ll examine the integration of demultiplexers in Field Programmable Gate Arrays (FPGAs) and Application-Specific Integrated Circuits (ASICs), highlighting efficiency and speed improvements. Advanced design considerations will be discussed for complex systems, followed by real-world case studies. Finally, we’ll conclude with insights into the future trends and technological advancements shaping demultiplexer technology in digital systems.

- Understanding Demultiplexers and Their Role in Digital Systems

- The Basics of Demultiplexer Logic: A Primer on Operation and Functionality

- Demultiplexer Types and Configurations: From 1:1 to 1:2^n Muxes

- Designing Demultiplexers with Logic Gates: A Circuit-Level Approach

- Demultiplexer Applications in Digital Systems: Use Cases and Examples

Understanding Demultiplexers and Their Role in Digital Systems

Demultiplexers are integral components within digital systems, serving as pivotal devices for directing signals to specific outputs based on the coded input binary value. These devices operate by using a selection line, or a combination of lines, to choose one output from among several potential ones. The demultiplexer’s functionality is realized through an intricate arrangement of logic gates, which include AND, OR, and multiplexer circuits. By encoding the input data and applying it to the selection inputs, the demultiplexer activates only the desired output line, allowing for precise control over data routing in complex systems.

In digital systems, the role of demultiplexers is multifaceted. They facilitate signal distribution in a manner that enhances system efficiency and minimizes signal interference between channels. The use of logic gates within these circuits allows for flexible design and scalability, enabling the demultiplexer to handle a wide range of data rates and input combinations. This flexibility is crucial in environments where multiple signals need to be processed independently or in parallel. By leveraging the principles of binary code, demultiplexers can direct signals with high accuracy, making them indispensable for tasks such as memory addressing, data routing in networks, and the control of complex digital systems.

The Basics of Demultiplexer Logic: A Primer on Operation and Functionality

In digital systems, a demultiplexer serves as a critical component that routes signals to specific output lines based on the value of an addressing code applied to its inputs. At its core, a demultiplexer operates by selecting one output line from among many possible outputs in response to a particular binary input pattern. This functionality is achieved through a combination of logic gates, which are fundamental building blocks in digital electronics. The basic structure of a demultiplexer includes a set of input lines, an addressing code input, and multiple output lines. The addressing code determines the path that a signal will take; each line of the output corresponds to a unique binary code.

The operation of a demultiplexer can be broken down into a series of logic gate functions. For instance, a multiplexer, which is essentially the inverse operation of a demultiplexer, selects one input line out of many and routes it to a single output. The demultiplexer takes the selected input from the multiplexer and distributes it to one of its outputs, depending on the binary code applied to its addressing input pins. The logic gates involved typically include AND gates for decoding the addressing code, OR gates for combining the selected signal with an inverting buffer, and sometimes XOR (exclusive OR) gates to handle the selection logic when the addressing code changes. Understanding the role of these logic gates is essential for grasping how demultiplexers function within digital systems, enabling the selective routing of signals which is crucial for efficient data handling and processing in complex circuits.

Demultiplexer Types and Configurations: From 1:1 to 1:2^n Muxes

In the realm of digital systems, demultiplexers are integral components that facilitate the routing of data signals from a single input to multiple outputs based on the coded addresses applied to them. These devices come in various types and configurations, catering to different needs within digital circuits. The simplest form of a demultiplexer is the 1:1 demux, which selects one out of two possible output lines corresponding to a single input signal and a binary address line. As the complexity increases, so does the capability of the demultiplexer; for instance, a 1:2^n demux can handle 2^n different outputs, where n represents the number of address lines provided. This scalability is achieved through the use of logic gates such as AND, OR, and multiplexer (MUX) gates, which are the building blocks of these devices. The configuration of a 1:2^n demultiplexer involves a combination of decoder circuits and MUXes. The decoder interprets the input address and activates one of the many possible output lines, while the MUX selects the appropriate output from all those activated by the decoder. As n increases, the number of possible outputs grows exponentially, allowing for more complex data routing in digital systems. This makes demultiplexers highly versatile and essential components in digital electronics, enabling efficient data handling and routing in a wide array of applications, from simple control circuits to complex communication systems. The choice of demultiplexer type and configuration depends on the specific requirements of the application, including the number of input signals, the desired number of output lines, and the addressable range. Logic gates play a crucial role in the design and operation of these devices, ensuring precise selection and routing of data streams based on binary addresses. Understanding the various demultiplexer configurations and their applications is key to designing efficient digital systems that can handle multiplexed data effectively.

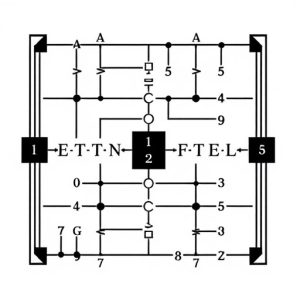

Designing Demultiplexers with Logic Gates: A Circuit-Level Approach

In the realm of digital systems, demultiplexers play a pivotal role in directing one of many input signals to the corresponding output line. A demultiplexer functions based on the inputs it receives, typically including an address or selector bit and the data signal. The design of demultiplexers using logic gates is a fundamental aspect of circuit-level engineering, leveraging the capabilities of these basic computational elements to achieve complex functionality. Logic gates such as AND, OR, NOT, NAND, NOR, XOR, and XNOR are the building blocks for constructing a demultiplexer’s logic network. The design process begins by understanding the binary address lines that dictate which output line should be activated. Each logic gate within the circuit evaluates these input signals, ensuring that only the desired output is active when its corresponding address code is present.

The integration of logic gates to create a demultiplexer involves careful planning to optimize performance and resource utilization. The choice of logic gates is critical as it influences factors such as power consumption, speed, area on the silicon chip, and reliability. For instance, a combination of AND and OR gates can be used to design a basic demultiplexer with a fixed number of output lines. This approach requires a clear understanding of binary mathematics and combinational logic design principles. As the complexity increases, so does the potential for optimization and innovation in the circuit’s layout. Advanced demultiplexers may incorporate multiplexer stages to enhance their versatility, further illustrating the importance of logic gates as the cornerstone of digital system design. By meticulously arranging these gates, designers can create efficient and scalable demultiplexing circuits tailored to a wide array of applications in digital electronics.

Demultiplexer Applications in Digital Systems: Use Cases and Examples

Demultiplexers play a pivotal role in digital systems by directing one input signal to one or more outputs based on the select lines’ binary codes. This function allows for efficient resource utilization and data handling within complex electronic circuits. A common application of demultiplexers is in memory addressing, where they assist in selecting specific memory locations from a multitude of possible addresses. For instance, in a computer’s memory system, a demultiplexer can determine which row or column of memory cells needs to be accessed, thereby enabling the precise retrieval or storage of data.

In communication systems, demultiplexers are integral for signal routing and distribution. They enable devices to receive specific data streams from a multiplexed set of signals transmitted over shared channels. For example, in local area networks (LANs), a demultiplexer can divide a high-speed data stream into separate channels, each carrying different information destined for various network devices. Similarly, in digital televisions, demultiplexers separate the composite video signal into individual components such as audio, video, and subtitle streams, allowing for their independent processing and decoding. These applications underscore the importance of demultiplexers in optimizing the performance of systems that rely on logic gates to perform complex operations at high speeds.